Data centers and AI chips are hitting limits in speed and efficiency. Can a 64 Gbps bi-directional interface change performance, cut power, and reduce chip size?

Data centers and chip designers face a challenge. They need to move more data at higher speeds while keeping power use and chip area in check. As workloads grow for AI and other compute applications, traditional interconnects are hitting limits in bandwidth, efficiency, and reliability.

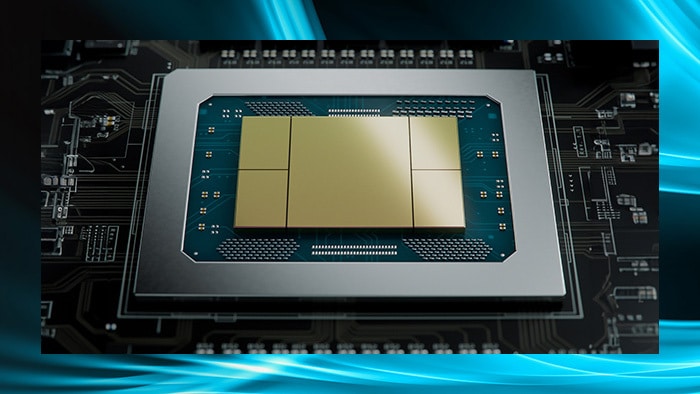

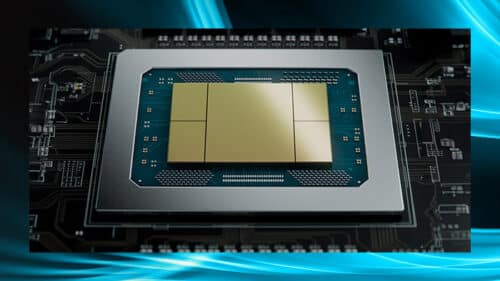

Marvell 64 Gbps Bi Directional Die to Die D2D Interface has been developed to address this. It is built on a 2nm process node and also available in 3nm. It gives next generation XPUs a way to connect compute dies. Each wire in the interface can carry 32 Gbps of two-way data, helping designers push performance without the penalty of higher energy use or larger silicon area.

The technology delivers over 30 Tbps per millimeter of bandwidth density, more than three times that of UCIe at comparable speeds. Its design reduces compute die area by up to 85 percent versus conventional interconnects, while adaptive power management lowers interface power use by up to 75 percent in normal operation and 42 percent under peak loads.

Marvell has built in reliability features such as redundant lanes and automatic lane repair to reduce bit errors and improve yields. To make adoption easier, the company offers not just the D2D PHY but a complete stack including the application bridge, link layers, and physical interconnect. This gives chip designers a platform for building the next wave of XPUs.

This product is aimed at chip designers and semiconductor companies working on next generation XPUs and processors. It is useful for teams designing AI accelerators, data center processors, and other compute systems that need faster die-to-die communication while minimizing power use and chip area.

“The 64 Gbps bi-directional D2D interface IP marks an industry first and reflects our commitment to pioneering technologies that enhance performance while reducing total cost of ownership for next-generation AI devices,” said Will Chu, senior vice president of Custom Cloud Solutions at Marvell. “D2D interfaces—which form the backbone of the communications networks linking silicon die within the same device–are fundamental to increasing the performance and efficiency of data center semiconductors and especially the rapidly growing custom computing segment,” said Baron Fung, Senior Director of Research at Dell’Oro.